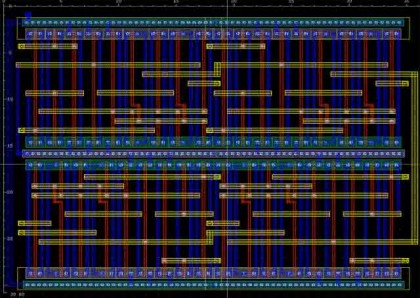

The objective of this report is to design a parallel 4-bit adder for low power consumption using 0.18 micron technology. The transmission gate implementation of the 4-bit ripple carry adder is chosen. Implementation is based on a bottom-up design methodology from schematic design of individual devices to integration. Critical paths are abstracted and optimized for low power dissipation. The schematic design is translated into prefabrication layout. Simulation of the schematic and layout realizations of the adder is performed and results are discussed. Performance is validated with specifications imposed by the target application.